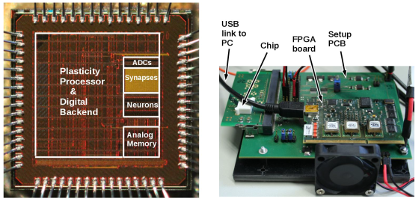

A compelling argument for neuromorphic spike-based emulation can be made when considering that learning (in particular, the simulation of synaptic plasticity) is by far the most time-consuming factor in simulations. Especially since it is one of the essential properties of neurons and synapses is that they can change over time, in particular as a result of learning. In the newly developed HICANN-DLS chip, we use an on-chip plasticity processing unit (NUX, see publications below, github) to control that change. The prototype chip features an array of 32 x 32 synapses, each of which stores a 6 Bit weight and analog correlation traces that relate pre- and postsynaptic events. The plasticity processor can use that information to implement various plasticity rules, with STDP being just one example. To allow scaling of this hybrid analog/digital approach, NUX has a vector unit with direct access to the analog and digital state of all synapses that can access up to 16 synapses of one row in parallel. The analog parameter storage (see publications below) used to configure and calibrate the neurons can also be controlled by the plasticity processor.

Hicann-DLS is a novel device that emulates spiking neural networks with physical models of neurons and synapses implemented in analog microelectronics. Networks on this chip are emulated approximately 1000-fold faster than biological real-time.

Demonstrating Hybrid Learning in a Flexible Neuromorphic Hardware System, Arxiv Link

Simon Friedmann, Johannes Schemmel, Andreas Gruebl, Andreas Hartel, Matthias Hock, Karlheinz Meier

Publication has been submitted to IEEE Transactions on Biomedical Circuits and Systems

Abstract: We present results from a new approach to learning and plasticity in neuromorphic hardware systems: to enable flexibility in implementable learning mechanisms while keeping high efficiency associated with neuromorphic implementations, we combine a general-purpose processor with full-custom analog elements. This processor is operating in parallel with a fully parallel neuromorphic system consisting of an array of synapses connected to analog, continuous time neuron circuits. Novel analog correlation sensor circuits process spike events for each synapse in parallel and in real-time. The processor uses this pre-processing to compute new weights possibly using additional information following its program. Therefore, learning rules can be defined in software giving a large degree of flexibility. Synapses realize correlation detection geared towards Spike-Timing Dependent Plasticity (STDP) as central computational primitive in the analog domain. Operating at a speed-up factor of 1000 compared to biological time-scale, we measure time-constants from tens to hundreds of micro-seconds. We analyze variability across multiple chips and demonstrate learning using a multiplicative STDP rule. We conclude, that the presented approach will enable flexible and efficient learning as a platform for neuroscientific research and technological applications.

Implementation and Characterization of Mixed-Signal Neuromorphic ASICs, Institute's Library

Andreas Hartel, Dissertation

An analog dynamic memory array for neuromorphic hardware, Institute's Library

Matthias Hock, Andreas Hartel, Johannes Schemmel, Karlheinz Meier

Abstract: We describe an array of capacitor based cells capable of storing analog voltages and currents for highly configurable large-scale neuromorphic hardware. A novel refresh scheme based on content-addressable memory as well as a slow and simple voltage ramp generator is presented. The circuits have been simulated in a 65nm mixed-signal low power process. Key characteristics are an area consumption of 175 μm2 and a power consumption of less than 125nW per stored value. A prototype chip has been designed and submitted for fabrication.

A highly tunable 65-nm CMOS LIF neuron for a large scale neuromorphic system, IEEExplore

Syed Ahmed Aamir, Paul Mueller, Andreas Hartel, Johannes Schemmel, Karlheinz Meier

Published in the Proceedings of 42nd European Solid-State Circuits Conference (ESSCIRC), September 2016

Abstract: We present the design and measurement of a continuous-time, accelerated, reconfigurable Leaky Integrate and Fire (LIF) neuron model emulated in 65-nm CMOS technology. The neuron circuit is designed as a sub-circuit of our highly integrated neuromorphic prototype chip, the “HICANN-DLS”. The design is geared towards testability and debug features, as well as area and power efficiency. Each neuron in the array integrates current from a multitude of input synapses onto an RC integrator within the synaptic input sub-circuit, where a variable resistor tunes the synaptic time constant. Linear transconductors convert voltage into an equivalent current as well as modeling the leak term, while a pulse generator circuit evokes a digital spike event. Our measurements show that the neuron successfully integrates input synaptic events ranging from a few nA to greater than 10 µA and tunes a wide range of tunable synaptic and membrane time constants. A higher membrane dynamic range of up to 1100 mV, and longer refractory times can be achieved, operating 1000 times faster than biological real-time. The design of the neuron simplifies calibration and reduces the mismatch, as multiple die measurements indicate. We demonstrate a one-to-one correspondence to software simulation for a typical computational model neuron. Due to the wide tunable range, the neuron is to be our general-purpose element of our second generation flexible neuromorphic platform for a variety of computational models.

From LIF to AdEx Neuron Models: Accelerated Analog 65 nm CMOS Implementation,

Syed Ahmed Aamir, Paul Mueller, Laura Kriener, Gerd Kiene, Johannes Schemmel, Karlheinz Meier

Published in Proceedings of the 13th IEEE Biomedical Circuits and Systems Conference (BioCAS), October 2017

Abstract: Here we present analog circuits emulating an Adaptive Exponential I&F (AdEx) neuron model developed for our second generation 65-nm CMOS neuromorphic hardware. Designed for an existing accelerated Leaky Integrate and Fire (LIF) circuit, the modular circuit architecture allows us to switch between LIF and AdEx neuron models and further to multiple-compartments. We describe our circuit implementation and the simulation results for adaptation and exponential sub-circuits. The neuron circuit specifications are compared with a targeted set of computational models. We show how addition of analog AdEx circuits let us qualitatively reproduce spike patterns known from cortical neurons.

A Mixed-Signal Structured AdEx Neuron for Accelerated Neuromorphic Cores, Arxiv Link

Syed Ahmed Aamir, Paul Müller, Gerd Kiene, Laura Kriener, Yannik Stradmann, Andreas Grübl, Johannes Schemmel, Karlheinz Meier

Accepted for publication in IEEE Transactions on Biomedical Circuits and Systems, May 2018

Abstract: Here we describe a multi-compartment neuron circuit based on the Adaptive-Exponential I&F (AdEx) model, developed for the second-generation BrainScaleS hardware. Based on an existing modular Leaky Integrate-and-Fire (LIF) architecture designed in 65 nm CMOS, the circuit features exponential spike generation, neuronal adaptation, inter-compartmental connections as well as a conductance-based reset. The design reproduces a diverse set of firing patterns observed in cortical pyramidal neurons. Further, it enables the emulation of sodium and calcium spikes, as well as N-Methyl-D-Aspartate (NMDA) plateau potentials known from apical and thin dendrites. We characterize the AdEx circuit extensions and exemplify how the interplay between passive and non-linear active signal processing enhances the computational capabilities of single (but structured) on-chip neurons.

An Accelerated LIF Neuronal Network Array for a Large Scale Mixed-Signal Neuromorphic Architecture, Arxiv Link

Syed Ahmed Aamir*, Yannik Stradmann*, Paul Müller, Christian Pehle, Andreas Hartel, Andreas Grübl, Johannes Schemmel, Karlheinz Meier

Accepted for publication in IEEE Transactions on Circuits and Systems I: Regular Papers, May 2018

Abstract: We present an array of leaky integrate-and-fire (LIF) neuron circuits designed for the second-generation BrainScaleS mixed-signal 65-nm CMOS neuromorphic hardware. The neuronal array is embedded in the analog network core of a scaled-down prototype HICANN-DLS chip. Designed as continuous-time circuits, the neurons are highly tunable and reconfigurable elements with accelerated dynamics. Each neuron integrates input current from a multitude of incoming synapses and evokes a digital spike event output. The circuit offers a wide tuning range for synaptic and membrane time constants, as well as for refractory periods to cover a number of computational models. We elucidate our design methodology, underlying circuit design, calibration and measurement results from individual sub-circuits across multiple dies. The circuit dynamics match with the behavior of the LIF mathematical model. We further demonstrate a winner-take-all network on the prototype chip as a typical element of cortical processing.

Electronic Visions Group – Prof. Dr. Johannes Schemmel

Im Neuenheimer Feld 225a

69120 Heidelberg

Germany

phone: +49 6221 549849

fax: +49 6221 549839

email: schemmel(at)kip.uni-heidelberg.de

How to find us