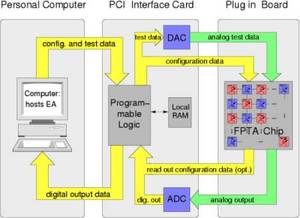

As already described in the Evolvable Hardware section, the ELECTRONIC VISION(S) group uses a hardware-in-the-loop setup for finding analog electronic circuits by means of hardware evolution. The evolution system consists of three main parts:

A standard PC hosts the software featuring the actual Evolutionary Algorithm, which uses fitness values of the old generation of candidate solutions to produce a new generation applying selection, mutation and crossover operations. Although the circuit responses of the candidate solutions are measured on the FPTA chip, it is here, in the software, where these measurements are evaluated and used to calculate the according fitness value.

An FPGA-based PCI card connects PC and FPTA. Since this card possesses some 'local intelligence' - i.e., a Field Programmable Gate Array (FPGA) - and local memory, it can be used as a real time extension to the computer's operating system. At the begining of an evolution run, the test patterns are stored in the local RAM. During evolution the whole test sequence for one candidate solution can be controlled by the FPGA. The test patterns are converted to analog voltages by a digital to analog converter (DAC) and the analog outputs of the FPTA chip are converted back to digital signals by means of an analog to digital converter (ADC).

The actual test of the candidate circuits takes place on the FPTA chip. Each circuit is downloaded to the chip and subsequently tested. Since the testboard is shared with other parts of the group, a little plugin-board is used to host the FPTA chip. Furthermore, it provides some additional analog circuitry to adapt the analog in- and output compliances of the testboard and the FPTA to each other.

This hardware-in-the-loop setup combines the flexibility of the software front end with the possibility of a real hardware test of the candidate circuits. The test system is fast enough to capture all interesting effects happening on the FPGA and helps to achieve high test rates of hundreds of candidate circuits per second.

Electronic Visions Group – Prof. Dr. Johannes Schemmel

Im Neuenheimer Feld 225a

69120 Heidelberg

Germany

phone: +49 6221 549849

fax: +49 6221 549839

email: schemmel(at)kip.uni-heidelberg.de

How to find us